Verilog HDL Basic Course inout port how to use in Testbench YouTube

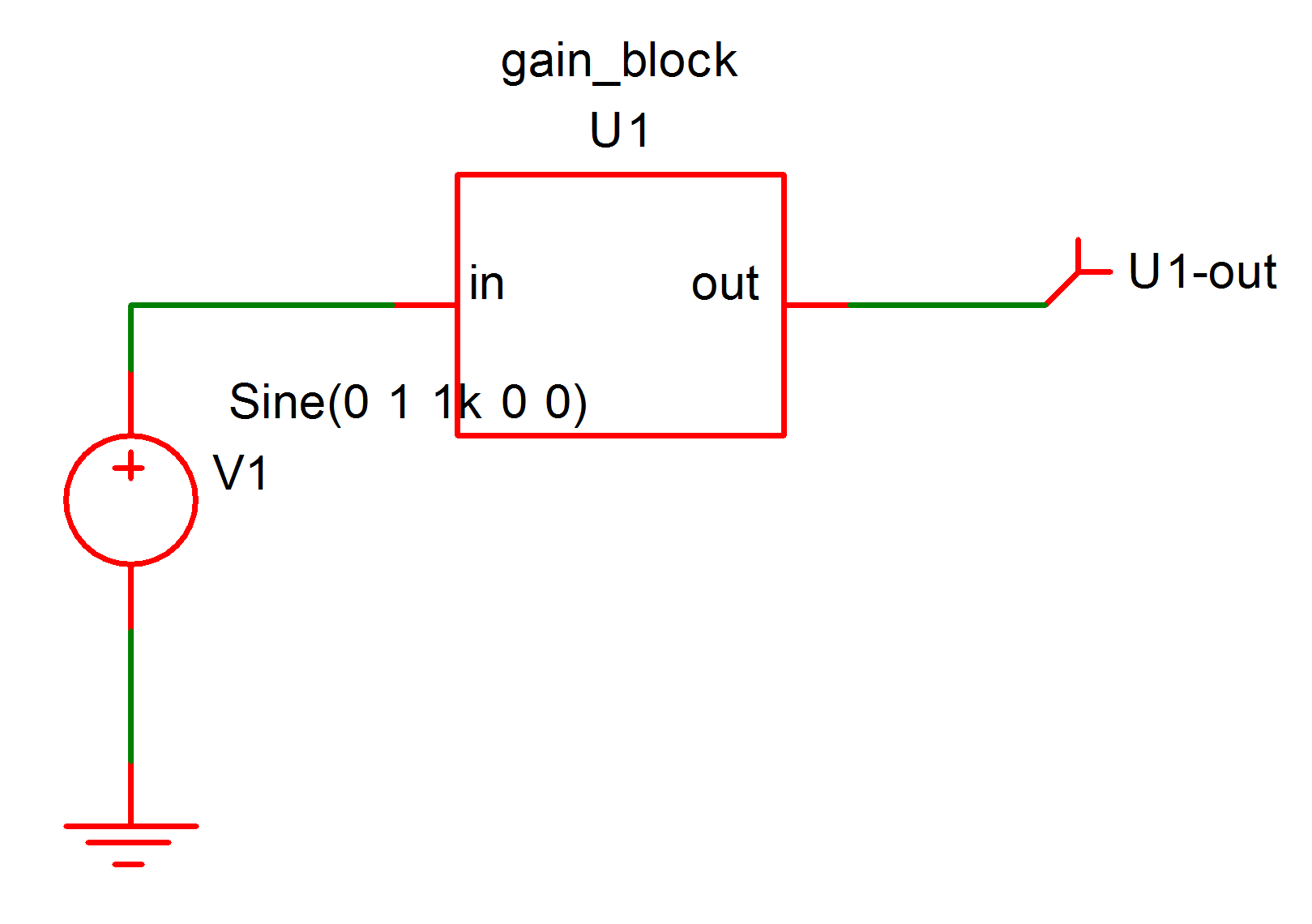

Modules are fundamental building blocks for structural and behavioral system description in the Verilog-A language. Ports provide module connectivity and allow communication between a module and its environment. When working on large designs, it is a common practice to decompose a system into a set of interconnected modules representing system.

Verilog Understanding multiple driver on bidirectional signal Stack Overflow

CAUSE: In a Verilog Design File or a VHDL Design File (), you declared the specified bidirectional port.Later, you made one or more value assignments to the port. However, these assignments indirectly or directly assign the port to itself, which results in an unsupported loop in your design.

Verilog Code For Serial Adder Subtractor Unit Markclever CLOUDYX GIRL PICS

www.micro-studios.com/lessons

Verilog A Reference Digital Gate

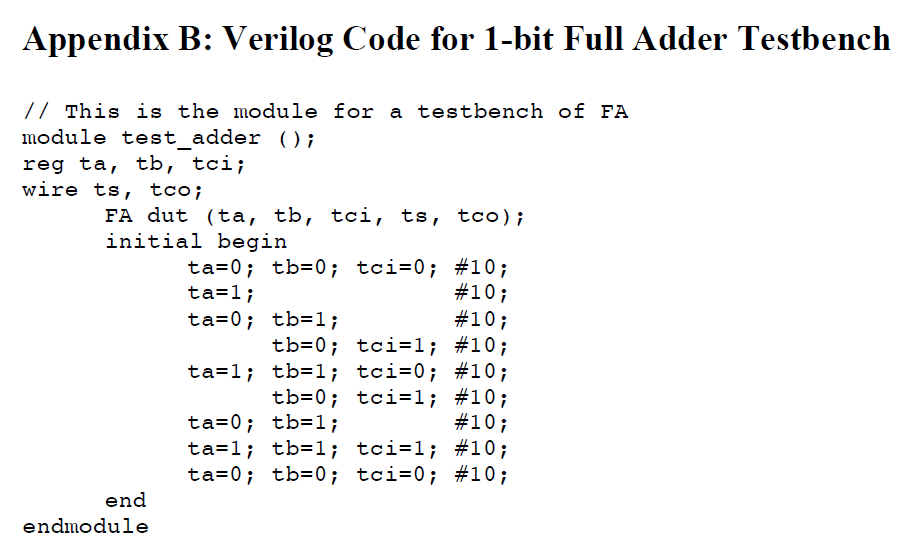

This post describes how to write a Verilog testbench for bidirectional or inout ports. This happens in special designs which contain bidirectional or inout ports such as I2C core, IO pads, memories, etc. In this post, I will give an example how to write testbench code for a digital IO pad.

Verilog code for Shift registers YouTube

I'm trying to use a bidirectional port in Verilog so I can send and receive data through it. My problem is that when I try to assign a value to the port inside a task, I keep getting an error. What is the correct way to assign a value to these types of variables? My code is as follows:

Verilog A Reference A Simple Device Model

#1 B bh_letters Junior Member level 3 Joined Feb 14, 2005 Messages 25 Helped 0 Reputation 0 Reaction score 0 Trophy points 1,281 Activity points 1,464 Hi, I have two modules and each has a bidirectional (inout) port. Now I need to connect these ports. Both the modules use the same signal to determine the direction of data flow.

8 The example Verilog code of a simple switch. Download Scientific Diagram

Bidirectional ports | inout port in VHDL and Verilog HDL#VLSI #Verilog #VHDL #DigitalDesign #InterviewQuestions

Test Bench Verilog aaaai2

How to assign value to bidirectional port in verilog? - Shashank V M Mar 28, 2021 at 6:17 Add a comment 2 Answers Sorted by: 2 You can't drive an inout directly as a reg. inout types need to be wire. So, you need a workaround. The workaround is creating a driver pin that shares the same wire as the module signal.

Bidirectional ports inout port in VHDL and Verilog HDL YouTube

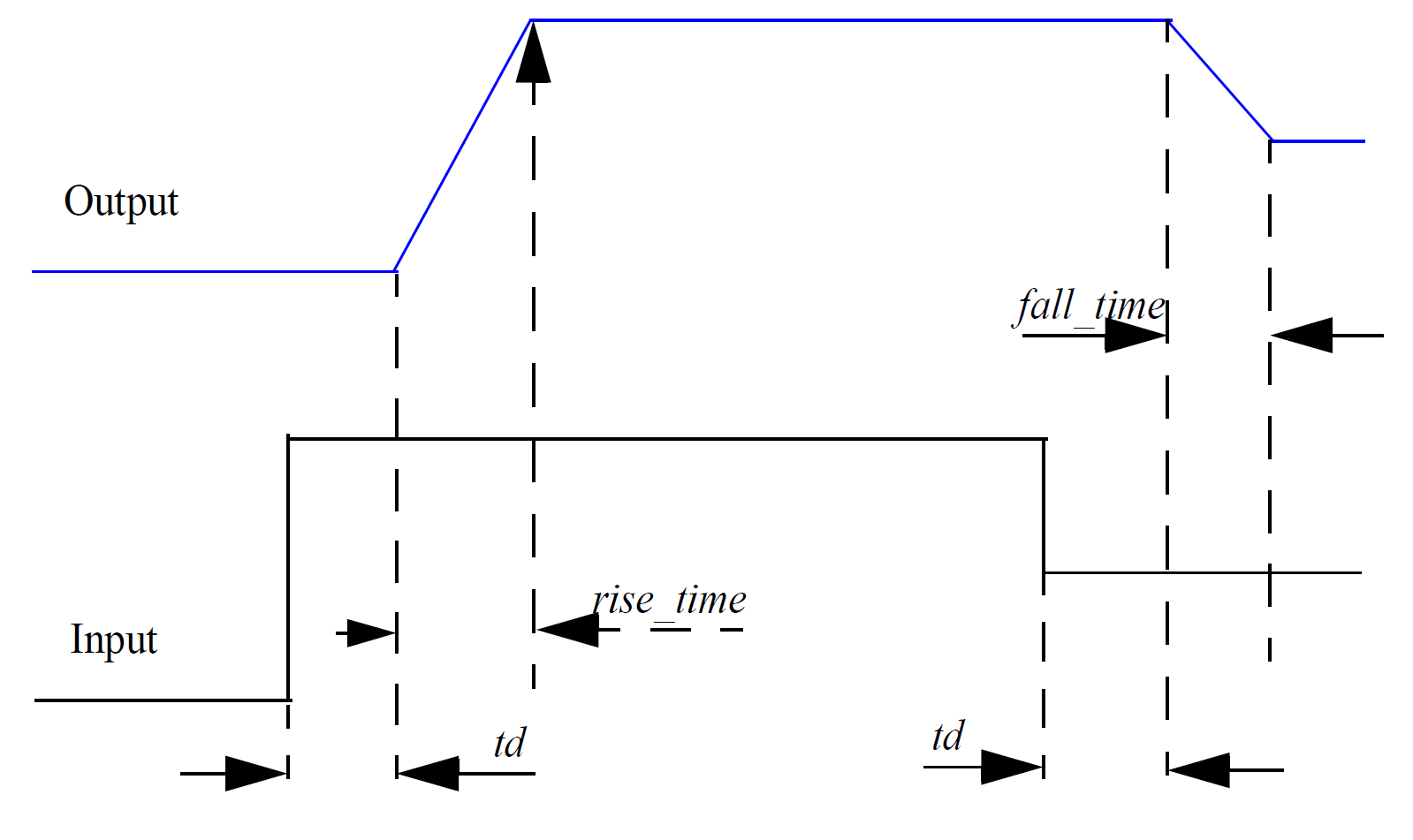

Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL. The value of OE determines whether bidir is an input, feeding in inp, or a tri-state, driving out the value b. For more information on using this example in your project, go to: How to Use Verilog HDL Examples

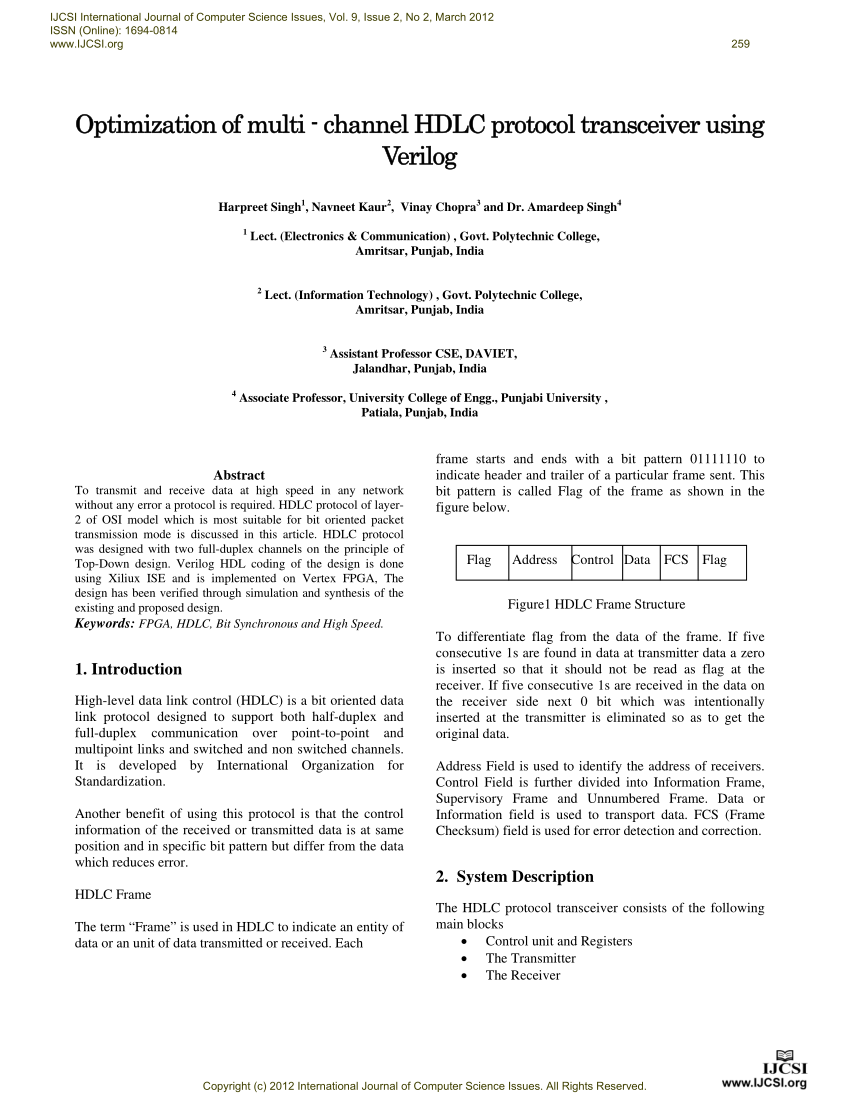

(PDF) Optimization of multi channel HDLC protocol transceiver using Verilog

Bidirectional port in verilog testbench Ask Question Asked 8 years, 4 months ago Modified 8 years, 4 months ago Viewed 21k times 3 How do we assign an input to a bidirectional port in Verilog testbench ? I have a design and an associated testbench. The relevant part of design is as follows:

Bidirectional Adjustment

Port Variations Verilog 1995 Verilog 2001 onwards Ports are a set of signals that act as inputs and outputs to a particular module and are the primary way of communicating with it. Think of a module as a fabricated chip placed on a PCB and it becomes quite obvious that the only way to communicate with the chip is through its pins.

Bidirectional Counter Àliter Group News Aliter Group

Verilog HDL: Customized 4-Port Crosspoint Switch. This design implements a 4-port crosspoint switch where all four ports are bidirectional. Each port is 8 bits wide and can be in tri-state mode, making it an input port. You can connect each port to any other port as an output or input.

Bidirectional Search in Python AskPython

If you must use any port because inout, Here are few things to remember: You can't read and write inout port simultaneously, hence kept highZ for reading. inout port can NEVER be regarding type reg. There ought becoming a condition at which itp should be written. (data in mem should be written when Write = 1 the should been able to read when.

FPGA digital design projects using Verilog/ VHDL How to write Verilog Testbench for

Modules. A Module is a basic building design block in Verilog and it can be an element that implements necessary functionality. It can also be a collection of lower-level design blocks. As a part of defining a module, it has a module name, port interface, and parameters (optional). The port interface i.e. inputs and outputs is used to connect.

Error (10663) Verilog HDL Port Connection error at led_demo.v(6) output or inout port "led

Electronic - Target of concurrent assignment or output port connection should be a net type; Port full register file from/to a verilog modue; Verilog: how to synchronously assign wire out with register; Electrical - Verilog assign result of module; Electrical - Verilog inout port

Verilog Module Instantiations

In the generated code, the bidirectional ports have the Verilog. For example, you can map a 32-bit bidirectional port to the Expansion Headers J6 Pin 2-64[0:31] interface. You cannot generate a Verilog or SystemVerilog test bench if there is a bidirectional port within your DUT subsystem. HDL Coder™ does.